March 13, 2019

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

December 31, 2018

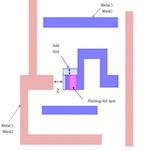

A detailed dive into how MBH strategies for litho hotspots have been enhanced to deal with double patterning at 20nm and below.

October 27, 2017

How to address increasingly complex patterning issues and debug them efficiently as design moves toward 12 and 10nm.

March 22, 2017

The equipment giant's Computational Process Control strategy takes a pragmatic approach to Industry 4.0 and is likely to influence EDA tools for incoming nodes.

January 4, 2016

The 10nm process node calls for the use of SOCV techniques during timing signoff to avoid leaving too much performance on the table.

November 26, 2015

The arrival of the 10nm process will impact the way that designers approach custom and mixed-signal layout. Cadence Design Systems has made changes to its Virtuoso environment that deploy increased automation support and electrically-aware layout to deal with the upcoming issues.

October 29, 2015

The 10nm process will see changes to multiple patterning that demands changes in the implementation flow, along with an increased focus on the effects of variability.

March 26, 2015

John Sturtevant looks at ongoing preparations for the incoming node and charts significant progress that has already been made.

February 11, 2014

Advanced tools are being applied to established nodes to produce advanced designs for volume markets.

January 20, 2014

It is not just a choice between EUV and multiple patterning for future nodes, but even between varieties of multi-mask technologies. How will you decide?