April 16, 2014

Reset is no longer simply an 'X' issue but also feeds into power optimization. Catching issues early greatly speeds verification.

April 16, 2014

Performing clock-domain crossing (CDC) checks on a flat database is difficult on complex SoCs. Hierarchy improves speed but calls for a smarter approach.

February 26, 2014

Increasingly complex state machines are driving the need for smarter ways of reporting errors such as deadlocks and unreachable code in the source RTL.

September 18, 2013

How all types of engineer can focus on X states that represent real risk, and set aside those that are artifacts of a design process.

July 3, 2013

Clock domain crossing bugs undermine the productivity gains of moving to block-based design, but can be tackled through hierarchical formal analysis.

May 14, 2013

RTL sign-off strategies ease SoC design and IP integration by enabling early analysis and optimization of CDC, power, X propagation, timing, and resetability issues.

May 7, 2013

Better upfront analysis can help avoid propagating errors from RTL into the netlist, and reveal a number of ways to improve the quality of your final design.

March 11, 2013

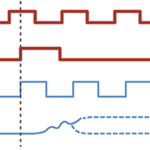

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

August 23, 2012

The verification challenge is best addressed by a combination of highly targeted tools, according to Pranav Ashar, CTO of Real Intent.