Closing code coverage with a hardware-aware HLS-to-RTL flow

High-level synthesis is gaining increasing traction for shrinking design cycles through higher abstraction and because of its ability to allow simulation’s execution 100-500X faster than at RTL. But as it has been adopted in markets such as computer vision and communications, closing code coverage has emerged as a tricky issue.

HLS typically uses C++ allowing for a more compact definition of the hardware’s intent, but users have often had to fall back on tools designed to enable software code coverage. By definition, these are not hardware-aware and therefore do not provide entirely reliable results.

Mentor, a Siemens business, is a long-standing pioneer in HLS through its Calypto suite. In a new article, the company describes how it has integrated Calypto and its Questa RTL simulation suite, to deliver that necessary hardware-aware analysis.

The paper describes the basics of code coverage, including the main metrics (Figure 1) and what those issues surrounding hardware awareness have been. It does this with particular reference to how CCOV (the Catapult Code Coverage Tool) sets about its work.

HLS-to-RTL code coverage

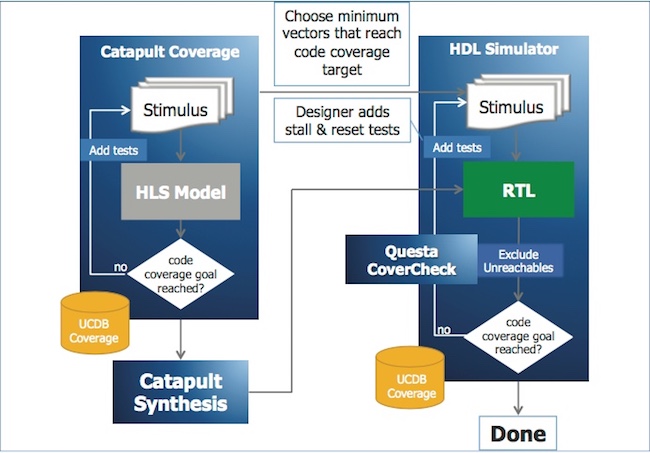

The HLS-to-RTL coverage flow has six main steps.

- The designer creates stimulus (tests) for the HLS model in C++ or SystemC.

- The designer runs CCOV to see if the coverage goals are reached by analyzing the Catapult coverage report. If not, the designer adds more tests. All coverage metrics are added to the Questa Unified Coverage Database.

- Catapult generates RTL from the C++ source code.

- The designer adds additional tests (see below) and uses the generated SCVerify infrastructure and makefile to simulate the RTL. If the designer uses the Questa simulator with code coverage turned on, all coverage metrics are added to the UCDB.

- If there is still any unreachable code, the designer can use Questa CoverCheck to help formally prove unreachability and provide directives to the simulator (or in UCDB) to exclude any unreachable code.

- If the RTL code coverage goals are reached, the verification is complete. If not, the designer adds more tests.

The coverage flow is also shown graphically in Figure 2.

Click on the following link to find out more in ‘Closing Coverage in a High-Level Synthesis Flow’.