Synopsys integrates Helic’s EM tools to tighten margins on mixed-signal, analogue and RF SoCs

Synopsys and Helic have integrated Helic’s VeloceRF RF device synthesis, RaptorX electromagnetic (EM) modeling and Exalto EM parasitic extraction and sign-off tools with Synopsys’ Custom Design Platform. The idea is to create a better way to account for the effects of EM fields during the layout and analysis of mixed-signal, analogue, and RF designs.

Better insights into the impact of EM fields should enable designers to reduce the design margins and guard-bands they usually include in their chips, leading to more efficient implementations. Key application areas for the flow include high-speed wireless communications and networking, Internet of Things devices, computing chips, and automotive SoCs.

The Synopsys/Helic tools integration puts a GUI within Synopsys’ Custom Compiler with which users can develop DRC-clean layouts of single- or multi-inductor spiral structures using VeloceRF. The VeloceRF tool creates schematic symbols and simulation models for use in Custom Compiler, and LVS rules for use with Synopsys’ IC Validator.

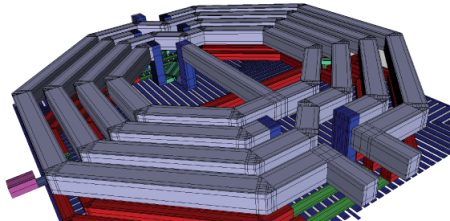

Helic’s tools use a 3D meshing algorithm to model capacitance, inductance and resistance more accurately

The flow also integrates Helic’s RaptorX, which enables analysis of EM effects during layout to reduce design iterations during signoff.

Helic’s Exalto EM parasitic extraction engine also works with Synopsys’ StarRC tool to provide a RLCk parasitic netlist for use in RF simulation. This enables Custom Design Platform users to do frequency-domain simulations of their circuits with HSPICE and then analyze the results with the Custom WaveView solution.

Yorgos Koutsoyannopoulos, CEO of Helic, said: “Bringing our EM-aware modelling, analysis, and signoff technology into the Synopsys Custom Compiler environment will enable mutual customers to avoid excessive margining and guard-banding and reduce the risk of silicon surprises.”

Further information

For more information on Synopsys Custom Compiler, visit www.customcompiler.info.

For more information on the Helic tool suite, visit www.helic.com.