Near-threshold clock control aims to improve processor efficiency

Finnish company Minima Processor is working on the first processor cores that will be customized to use its timing-control technology to push supply voltages into the near-threshold zone and so reduce active power consumption.

The company is working with ARM to produce a version of the Cortex-M3 intended to operate reliably at lower voltages than would be possible with the standard synthesized core.

“Achieving a 15-20x reduction in energy in an IoT SoC is an impressive feat, and one that will open up a whole new set of IoT applications,” says Phil Burr, director of portfolio product management at Arm.

Minima does not intend to limit its work to Arm cores. CTO Lauri Koskinen said the business model is to supply hard macros that combine processor cores with its own timing-control logic that lets DVFS-enabled processors operate much closer to their minimum operational supply voltage.

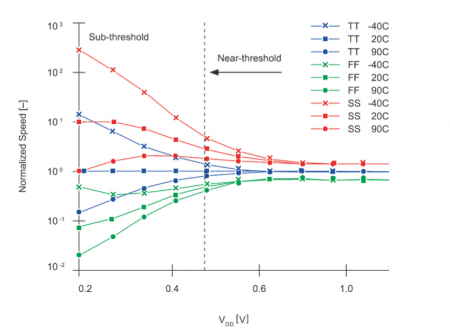

Image Timing variation increases dramatically close to the threshold voltage

The key problem of near-threshold digital design is one of timing variation. As the supply approaches the threshold voltage timing predictability worsens. As a result, although reducing voltage offers a quadratic improvement in power consumption, it becomes difficult to guarantee that a core will function correctly. Slow transistors in a critical path will cause errors because they fail to deliver an answer within the clock period. One way around this is to use large voltage margins, but these result in higher power consumption.

One approach used by the Razor technology developed at the University of Michigan is to detect errors caused by too low a voltage and to rerun the affected cycles. The Minima technology delays clock edges on critical paths using time borrowing to avoid having to rerun cycles.

Koskinen said the technology employs linked control loops. One is a software-controlled loop to adjust supply voltage over a long time horizon and the other is a faster hardware loop to adjust to faster events, such as sudden IR drops. If the hardware loop timing sensors detect a potential instantaneous problem, it invokes time borrowing to delay the next clock edge. By pre-empting voltage drops, Minima argues it is able to avoid the problems of having to rerun cycles.

Minima Processor announced in June it raised approximately €5.5m Euros ($6.4m) in funding from Aalto University, CFT Nordic Investment Center, Lifeline Ventures, VTT Ventures, and angel investors.