Synopsys updates custom design tools for the finFET age

Synopsys is updating its custom design tools to make working with finFET based processes easier.

Whereas adjusting a transistor’s characteristics in a planar process simply involves changing the shape of the polygons that define it, the quantized nature of finFETs means that if you want to change a finFET transistor’s channel width you need to lay out multiple fins in parallel, while if you want to change its channel length you need to stack fins in series. Adjusting both characteristics at once can mean designing complex arrays of fins.

According to Dave Reed, director of marketing for the AMS group at Synsopsys, this complexity “is getting to the point where designers find it hard to visualize what is happening.”

Creating matched transistors, for example to ensure equal drive strengths on differential-pair single lines, usually means interdigitating the two devices, which becomes complex when each is made up of an array of fins. Advanced processes also come with highly restrictive design rules, for example demanding that routes can only go in one direction on certain layers, which further complicate the custom designer’s job.

Reed estimates that it take three times more effort to design with a finFET process than with its planar predecessors.

“The world has changed with finFET, but because things are more fixed it lends itself to automation.”

The new Custom Compiler has been structured as a visual design tool, enhanced with automation and analysis to ease repetitive tasks (like wiring up arrays of fins), and ensure designers are alerted to any issues their design might face as they go.

“At heart, this is a polygon pushing tool,” said Reed, “we’ve just layered some automation on it.”

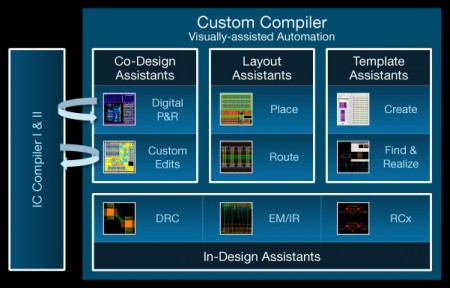

This automation comes in four major parts.

Figure 1 Four forms of automation ease custom design with finFET processes (Synopsys)

Layout Assistants speed layout by offering visually-guided automation of placement and routing. The router is ideal for connecting finFET arrays or large-M factor transistors. It automatically clones connections and creates pin taps. The user guides the router with the mouse and it fills in the details automatically. The placer uses a new approach to device placement, which enables the user to make successive refinements, offering placement choices but leaving the layout designer in control of the results. The tool’s visual design paradigm means that this happens without the designer having to write constraints.

Template Assistants help designers reuse existing know-how by making it easy to apply previous layout decisions to new designs. Template Assistants learn from the work done with the Layout Assistant’s placer and router. They intelligently recognize circuits that are similar to ones that have already been completed and enable users to apply the same placement and routing pattern to new circuits. Custom Compiler also includes templates for commonly used circuits, such as current mirrors, level shifters and differential pairs.

In-Design Assistants catch physical and electrical errors before signoff verification by including a design rule checking engine, electromigration checking, and resistance and capacitance extraction. Custom Compiler’s extractor is based on Synopsys’ StarRC engine.

Co-Design Assistants combine IC Compiler and Custom Compiler into a unified solution for custom and digital implementation, so that users can freely move back and forth between the two tools to refine their designs. IC Compiler users can do full-custom edits on their digital designs at any stage of implementation. Custom Compiler users can get IC Compiler to implement digital blocks in their custom designs. This ‘round trip’ capability means that all changes are synchronized between the digital and custom databases.

Partner endorsements

Custom Compiler has been in development with partners, as well as Synopsys’ internal IP development team, for at least a year now.

TSMC has certified the tool for use with its emerging 7nm and 10nm finFET processes. This means designers can use Custom Compiler to work with advanced process features such as track-pattern support, coloring assistance, electrical-aware layout, EM/IR checking and parasitic-aware analysis.

“We have worked closely with Synopsys to certify Custom Compiler for the 10nm process node and 7nm early design starts,” said Suk Lee, TSMC senior director, Design Infrastructure Marketing Division. “A PDK is available to support Custom Compiler for mutual customers on TSMC finFET process nodes, through the iPDK standard.”

Asahi Kasei Microdevices (AKM), which provides sensors and mixed-signal designs for automotive and consumer products, is switching to Custom Compiler to speed up the design process.

“We selected Custom Compiler to replace our previous solution,” said Takanobu Hamazaki, general manager of AKM. “It is easy to adopt and customize to our needs due to its open environment, based on open standards. By automating routine tasks, Custom Compiler will help us meet our custom design time reduction goal.”

AKM uses Custom Compiler’s Template Assistants, which enable designers to create complex layout topologies and save them as patterns for reuse, to carry forward work it has already done to create customized features and utilities into the new environment. Custom Compiler uses TCL and Python, easing further customization.

GSI Technology, which designs memory for networking, military, medical and automotive applications, has also switched to Custom Compiler, in part for its ability to make designing with finFETs more productive. Custom Compiler’s ability to analyze issues such as electromigration and IR drop during layout also informed their decision.

GSI has adopted Synopsys’ HSPICE, FineSim, StarRC and IC Validator tools to fill out their finFET-ready custom design flow.

Randy You, CAD manager at GSI, said: “The In-Design Assistants in Custom Compiler enable us to deal with the design complexity of the finFET process by reducing unnecessary design iterations and improving productivity.”

STMicroelectronics is using Custom Compiler to design IP blocks in its 28nm FD-SOI process.

Cyril Colin-Madan, design platform director at STMicroelectronics, said: “ST has adopted Custom Compiler for 28nm FD-SOI standard cell and memory layout. A key factor in our decision to adopt it was the improvement in productivity. Custom Compiler’s Template Assistants make it easy to apply previous layout decisions to new designs, which helps us shorten layout tasks from days to hours for a typical cell.”