Mentor builds out verification IP for memory

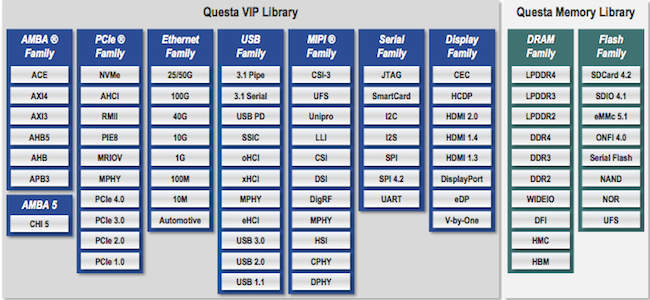

Mentor Graphics today (February 29) launched a new verification IP (VIP) library with 16,000 memory models, joining its existing Questa VIP protocol library. The models address what studies have show to be a ‘Top 4’ concern among verification engineers, the increasing length of time needed for testbench development.

The library includes models for all major manufacturers, searchable by product number, and is compliant with multiple standards including the Universal Verification Methodology (UVM), System Verilog, the Unified Coverage Interoperability Standard (UCIS) and the proposed portable stimulus standard from both Mentor and Cadence Design Systems.

Mentor’s VIP will also be the first to support the high performance HyperBus flash and DRAM interface from Cypress Semiconductor (Spansion).

The library is, as you would expect, fully compatible with Mentor’s Enterprise Verification Platform, though the models can be used with other UVM and SystemVerilog-based simulators.

The models were all built in-house by a Mentor team based near Noida, India. The work began about two years ago.

The VIP market is one of the fastest growing in the verification sector, valued by Gartner Dataquest in the region of $110M-$130M. Outsourcing complexity and reducing risks are driving the growth.

“In the data we’ve seen from the Wilson Research Group study, testbenches are about a quarter of the effort, and in there, you’ve got two components: writing the VIP and writing the tests,” explains Mark Olen, product marketing manager in Mentor’s Design Verification Technology division.

“If you take the example of what we saw among systems companies with the move to PCI Express, that was kind of a tipping point for them. They were dealing with a protocol so complex that writing the VIP was likely going to take more time that writing tests. So they decided, ‘We’ve got to outsource this.'”

Olen said that Mentor’s success in creating VIP that gave customers more time for actual test led them to encourage the company to enter the memory VIP market.

There is some debate whether VIP is used simply to cut time-to-market. Rather, as Olen himself believes, many customers use the time they save not developing VIP themselves to write and run more test cases.

The memory models are available to use pre-configured and pre-parameterized out-of-the-box, and also in conjunction with custom configuration files. One new feature is the ability to use the models in dynamic ‘on-the-fly’ configurations.

“We think the FPGA guys are particularly going to love this because a lot of memory there is done off-chip because it’s so cost sensitive. They want to define a system architecture early on, but wait until the very last minute before choosing memory, so they can find the cheapest,” said Olen.

“With this feature, you no longer have to write, say, three or four different tests for each configuration. You can write just one and then at various break points swap in models from different vendors. You don’t have to go back and keep re-running the simulation.”

Availability on the new library is immediate.