IBM and friends at 7nm: breakthrough or science project?

IBM and its partners – Samsung, GlobalFoundries and the State University of New York at Albany – have fabricated the first functioning chip at the 7nm node but only by layering in a series of innovations for beyond 10nm that may still make potential adopters wary. In short, big NRE questions remain.

The important thing to understand about the consortium’s breakthrough is that it has required the simultaneous introduction of three new techniques:

- The ‘commercial’ use – finally! – of EUV lithography.

- Silicon germanium replacing silicon in the transistor channel.

- The application of self-aligned quadruple patterning.

Under effective lab conditions, the results are impressive. SiGe’s use allows transistor stacking at a tighter pitch of 30nm (vs. 42nm at 14nm) and overall IBM is claiming a near 50% reduction in surface area over 10nm, with a resulting 50% improvement in power and performance. Moore’s Law lives. But at what cost?

Will the investment needed to deploy these techniques commercially outweigh the benefits of the shrink? One major innovation at a new node is considered a tough challenge – here we are looking at three.

Costing 7nm remains a challenge

The industry’s move from 28nm to 20nm raised questions over the true economies available from moving to the latest process node under non-classical scaling (although many would argue that 20nm adoption is now running ahead of earlier pessimistic forecasts).

In addition, this 7nm announcement comes only days after a claimed leak out of Intel suggested it has been forced to postpone the introduction of 10nm chips because of manufacturing challenges at that earlier but still incoming node.

A design manager has to wonder about the combined 7nm risks of depending on a new light source, designing with a new material (notwithstanding IBM’s extensive earlier use of SiGe itself), and adding yet another layer of patterns. The sums look tough. Tough to do and tough to stomach when some likely very high estimates tumble out.

Moreover, even allowing for an apparently successful use of EUV lithography equipment by the IBM consortium, it’s worth bearing in mind that has repeatedly failed to meet target introduction dates for commercial deployment. The Albany fab where the 7nm chip was made neighbors the main global EUV R&D research center, and all the indications are that prototype EUV steppers were used.

Making a case for 7nm

At the same time, there are some positive things to note. Foremost among those perhaps is the fact that IBM needs 7nm to happen.

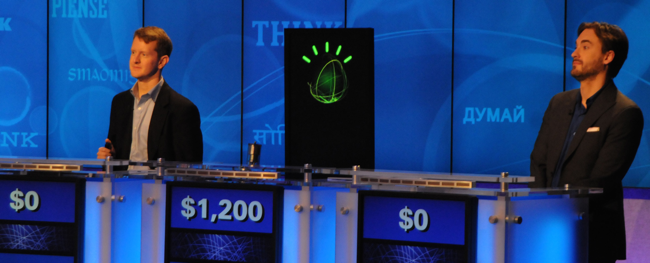

At one level, its semiconductor business depends on pushing out new processes against which IBM can sell process IP (and, we now hear, EDA tools), given Big Blue has completed its exit from actual chip manufacturing. Meanwhile in broader terms, 7nm is important to the company as a way of powering the HPC applications it wants to build based on its server technology and Watson cognitive computing system.

IBM isn’t simply doing this for bragging rights… one hopes. Nor, as they look to assert foundry technology leadership against TSMC, is Samsung or GlobalFoundries. After all, TSMC – which is yet to show off a 7nm chip – has been talking about a 7nm ramp starting as soon as 2017.

However, for the consortium to capitalize on this week’s achievement, it still needs a lot to happen. Here are a few examples we should all now look for before the end of 2015:

- This Summer will be bookended by Semicon events in the US and Taiwan. Something that instills greater, broader confidence in EUV at either would be a big help.

- DAC is behind us, but the post-Labor Day period will see a number of IP and EDA related events, perhaps most significantly ARM Techcon. What will be said about 7nm at those? The more the better. It’s still all about the ecosystem.

- And, of course, there is IEDM in December, the key technical conference for manufacturing innovation. If you want to convince hardcore design managers that 7nm is worth preparing for, that more than any other is the time to make your case.

Ask any parent: Baby steps can be tremendously exciting. But you also need to recognize them for what they are. Making the first 7nm chip is a notable achievement, but it remains one contingent upon a great deal more. Think of it initially as the shift to walking and chewing gum at the same time.