Mentor tool streamlines multi-corner parasitic extraction

Mentor Graphics has launched an SoC parasitic-extraction tool, applying enhancements the company has developed that are able to deal with the more complex electrical environment of finFET-based processes.

Calibre xACT is derived partially from the technology used in the xACT 3D tool launched in 2010. The use of this technology maintains the company’s focus on a deterministic field solver approach rather than use the random-walk algorithms of other tools aimed at SoC sign-off, which were introduced to try to control runtimes but which can introduce problems of a fraction of the predictions differing significantly from actual results.

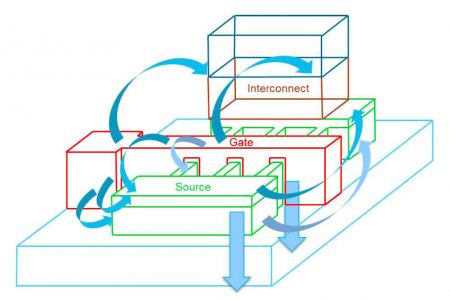

In xACT, the field-solver is used to deal with situations such as the highly complex parasitics environment of finFET-based processes, where capacitive interactions between vertical fins and densely packed interconnect are far more intricate than with planar processes. For the metal interconnect that does not fall into the middle-end-of-line (MEOL) parts of the design, such as the upper metal interconnect, the tool switches to a table-based approach for higher speed.

Image FinFETs present complex extraction scenarios

The tool uses heuristics to switch between extraction techniques based on the layers being analyzed – using simpler algorithms for situations where it determines it can use the table-based approach and reserving the field solver for device-level interactions

To streamline the use of data from a design, the tool extracts parasitics from the layout into a core database and then refers to that to build the individual net lists needed for different kinds of analysis, such as resistance-only net lists for electromigration predictions. Designers and verification engineers can manipulate the net lists to simplify them for performance, such as reducing the multiple resistances and interacting capacitances of via arrays to a couple of lumped parameters.

“Someone doing timing sign can accommodate a large amount of reduction,” said Carey Robertson, product marketing director. “Most of the time spent in parasitic extraction is geometric processing: chopping the design up and analyzing the geometric interactions. We do this once and do the actual math at the end – computing the geometric interactions into Rs and Cs.”

Multi-corner speedup

Robertson said Mentor’s approach to the problem deals better with the multiple-corner analyses now needed to handle layouts that use multiple-patterned lithography as well taking different operating temperature points into account. The implementation suffers only a 15 to 20 per cent runtime increase for each additional corner without spurious differences caused by changes in the results when new random-walk results are generated for each additional corner by tools that use stochastic techniques.

In one test by customer Cypress Semiconductor, the tool was used to generate analyses of 15 corners with a runtime increase that is far lower. “The big winner is multi-corner results within a single run,” said Bo Gao, senior engineering director at Cypress.

Gao said the company runs extensive tests when evaluating full-chip parasitic-extraction tools. “Our QA group has to test against a field solver and we use test structures that we know can cause RC extraction to fail.

“We’ve qualified xACT on multiple platforms,” Gao added, including processes used for memories, the company’s programmable mixed-signal microcontrollers, automotive parts. On most of these designs, Cypress will run four-corner analyses at least.

For finFET processes, Robertson said customers are likely to work with eleven corners – adding six just to deal with the variations caused by double patterning.

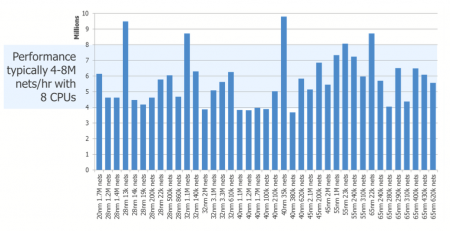

Image Extraction performance on different designs using eight CPUs

In common with other vendors’ recently launched tools, Calibre xACT is designed to run across multiple processors. Mentor said the tool extract can extract between 4 million and 8 million nets per hour across 8 CPUs on planar processes, allowing a full chip with 20 million nets to complete overnight. Larger designs can be handled with faster turnaround time by adding additional CPUs.

To provide better performance scaling, Mentor decided to use net-based parallelism rather than tiling. Each net is sent to a single processor and run there rather than having the equations for a net split across multiple processors, a technique used by some other tools.

For fine levels of control in custom-design flows, designers are able to select the specific parasitic model they want on a net-by-net basis, focusing attention on critical paths but reducing simulation time for other, less critical nets. For example, designers can select: distributed RCC (with coupling capacitance); RC (without coupling capacitance); C-only; or R-only.

Designers can also control extraction by layer. For example, to reduce simulation time in analyzing the parasitic effects for large power and ground nets, designers can extract supply and ground nets that report only the via resistances and exclude metal-layer resistance. As vias contribute the bulk of the resistance to the power and ground network, this can enable faster simulation.